Immer wieder führen programmierte FPGAs beim Boundary Scan zu Problemen - hier finden Sie die Lösung..

Grundlagen

Ein geladener/konfigurierter FPGA führt in vielen Fällen im Zusammenspiel mit dem Standard BSDL zu vielen Fehlern oder sogar Kettenabbrüchen während dem BSCAN.

Hintergrund ist, dass durch die Konfiguration die PIN Eigenschaften verändert werden.

Die Hersteller (Xilinx/Altera/Lattice) bieten aus diesem Grund in Ihren Programmiertools Optionen zum Erstellen von speziell angepassten BSDLs an.

Ich empfehle jedoch aufgrund von folgenden Punkten auf den Einsatz dieser BSDLs zu verzichten

- Load-Veränderung kann zur BSDL Änderung führen

- Höherer Aufwand für die Erstellung

- Verringerung der Testabdeckung und Diagnose !!

Viele Anwender verhindern die Konfiguration des FPGAs auch durch Jumper oder sogar durch das Löschen vor dem Test und dem erneuten Programmieren über ein SVF,JAM,Staple nach erfolgreicher Prüfung.

Diese Möglichkeit führt jedoch zu einer nicht zu vernachlässigen Verlängerung der Prüfzeit...

Eine bessere Lösung ist deshalb die Konfiguration nur zeitweise außer Betrieb zusetzen, dies ist wie folgt möglich

Altera-FPGA

Durch das Laden der Instruktion „Config_IO“ und einer kurzen Wartezeit (~1s) kann die Load außer Kraft gesetzt werden.

Hierzu kann im EGS der CASCON Software des Herstellers Göpel folgender Eintrag vorgenommen werden

(CASCON

(Begin

load Dx, config_io;

irshift;

wait 1000;

tapreset;

)

)

Anmerkungen:

- Nach der Entladen der Load, muss zwingend ein "TAPRESET" oder alternativ ein "load Dx, Bypass","load Dx, Sample","load Dx, Extest" eingefügt werden.

Dies ist notwendig da das config_io Register eine sehr große Anzahl von BSCAN Zellen aufweist und dies alle nachfolgenden Tests erheblich verlängert. - Bei einigen Typen (Cyclone III) kann es evtl. notwendig sein, vorher die Instruktion „Factory“ oder „ACTIVE_DISENGAGE” zu senden

Xilinx-FPGA

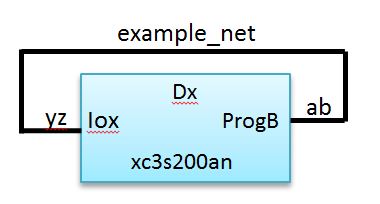

Durch das Tooglen des ProgB Pins kann die Load bei Xilinx-FPGAs ebenfalls außer Kraft gesetzt werden.

Da der ProgB jedoch nicht direkt getoggled werden kann, muss das togglen über einen angeschlossen Pin erfolgen – bei allen bisher mir bekannten Designs war dies möglich.

Hierzu kann im EGS der CASCON Software des Herstellers Göpel folgender Eintrag vorgenommen werden

-----------------------------------------------------------------

(BSCANMODIFICATIONS

(NET 'example_net' drive_low) --> avoid FPGA configuration

-----------------------------------------------------------------

(CASCON

(STEP_1

enable(Dx:#yz);

drshift;

dl (Dx:#yz);

drshift;

dh (Dx:#yz);

drshift;

dl (Dx:#yz);

)

-----------------------------------------------------------------

Anmerkungen:

- Aus bisher ungeklärten Gründen hat es bei einem mir bekannten Design umgedreht funktioniert, d.h. low und high vertauscht.

Lattice-FPGA

Bisher keine Lösung gefunden - Doku wird sobald Erkenntnisse vorliegen ergänzt.